Open access Journal International Journal of Emerging Trends in Science and Technology

# Design of Low Power Transversal FIR Filter For VLSI Signal Processing Applications

Authors

Soumee Sharmeela Pattnaik<sup>1</sup>, Ritisnigdha Das<sup>2</sup>, Siba Kumar Panda<sup>2</sup>

<sup>1</sup>M.Tech Scholar, CUTM, Jatni, Bhubaneswar, Odisha, India

Email: Soumee04@gmail.com

<sup>2</sup>Assistant Professor, Department of ECE, Centurion University of Technology & Management,

Bhubaneswar, Odisha, India

Email: *ritisnigdha.das@cutm.ac.in*, *panda.sibakumar08@gmail.com*, *siba.panda@cutm.ac.in* **Abstract**

An efficient novel technique of synthesis of a low arithmetic complexity, linear phase low pass FIR filter is proposed .The output response is modeled using trigonometric functions of frequency and its slopes. This approach has the advantages of ease of computation of the impulse response and reduction in the Gibb's phenomenon. The synthesized filter proves to be a good alternative to the existing FIR filters. This paper deals with the design of 16-tap FIR filter and proposed work has been done using Xilinx ISE 9.2i evaluating the performance by the synthesis report and shown the synthesizes RTL schematic along with the simulation results.

Keywords: FIR, Transversal, VHDL, Digital Signal Processing, VLSI Signal Processing.

#### 1. Introduction

Depending on the response of the system, digital filters can be categorized as: Finite impulse response (FIR) and Infinite Impulse Response (IIR) filters Although FIR filters, mainly require higher no. of taps than IIR filters to obtain similar frequency characteristics.FIR filters have linear phase characteristics which guarantees stability and are easy to implement with multipliers, adders and delay elements, so they are extensively used. The number of taps in digital filters varies according to applications. . In commercial filter chips with the fixed number of taps, zero coefficients are loaded to registers for unused taps and unnecessary calculations have to be performed. To diminish this problem, the FIR filter chips provide variable-length taps that can be widely used in many application fields. However, these FIR filter chips use memory, an address generation unit, and a module unit to access memory in an efficient manner. Since the architecture proposed only requires several Multipliers, registers, and adders, the number of gates can be reduced significantly than existing chips. In, general, FIR filtering is described by a simple convolution operation as expressed in the equation

$$y(k) = \sum_{k=0}^{N-1} h(k) \cdot x(n-k)$$

Where x[n] represent data input, y[n] represent filtering output, and h[n] represent a coefficient, respectively and N is the filter order.

#### Advantages of FIR OVER IIR

FIR can be designed with exact linear phase.FIR filters are always stable with quantized coefficient. It can be realized in both recursive and nonrecursive structures. When FIR filters are implemented on finite–word length digital system they give free limit cycle oscillations The above benefits makes FIR filters attractive enough to be implemented onto a large no. of system. For frequency response, FIR filters have higher order than IIR filters making FIR filters expensive.

#### 2. Related work

Achinta Roy(2014)<sup>[3]</sup> proposed a technique of generic n-tap Fir filter, the thesis was proposed on design and structure and occupied silicon space, needed for Implementing in fpga the result was full configurable using generic parameters.

2015

Yan Sun and Min Sik Kim<sup>[5]</sup> presented an approach to implement a high-performance 8-tap digital FIR (Finite Impulse Response) filter using the Logarithmic Number System realize a fast FIR filter by utilizing the Logarithmic Number System, which allows a simple implementation of multiplication using a fixed-point adder.

Fábio Fabian Daitx, 2008<sup>[4]</sup> This work proposes an VHDL generation software for optimized FIR filters. In this paper a near optimum algorithm for constant coefficient FIR filters was used. This algorithm uses general coefficient representation for the optimal sharing of partial products in Multiple Constants Multiplications (MCM). The developed tool was compared to Matlab FDA toolbox.

Abul Fazal Reyas Sarwar, Saifur Rahman<sup>[2]</sup> provided the principles of Distributed Arithmetic, and introduce it into the FIR filters design, and then presents a n-Tap FIR low-pass filter using Distributed Arithmetic. The implementation of FIR filters on FPGA based on traditional method costs considerable hardware resources, which goes against the decrease of circuit scale and the increase of system speed.

Deepshikha Bharti , K. Anusudha<sup>[7]</sup>, High speed Finite Impulse Response filter (FIR) is designed using the concept of faithfully rounded truncated multiplier and parallel prefix adder. A transposed form of FIR filter is implemented using an improved version of truncated multiplier and parallel prefix adder. Multiplication and addition is frequently required in Digital Signal Processing.

# **3.FIR Filter-VHDL**

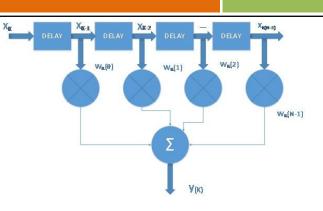

### 3.1 Traversal Filter

The most commonly used structure in implementing adaptive filters is the traversal structure. the traversal can be divited into two main parts the filter part and update part. the filter output is calculated as a linear combination of the input sequence x(n-k)=0,1...N-1 composeed of delayed samples of x(k). The traversal filter structure is, therefore, a linear temporal filter that processes the temporal samples of its input signal x(k) to produce modified output y(k)

An N-Tap transversal was assumed as the basis for this adaptive filter. Practical considerations are made to determine the value of N. An FIR filter was chosen because of its stability. The use of the transversal structure allows relatively straight forward construction of the filter.

Fig 1: Transverse FIR filter.

As the input, coefficients and output of the filter are all assumed to be complex valued, and then the natural choice for the property measurement is the modulus, or instantaneous amplitude. If y(k) is the complex valued filter output, then amplitude is denoted by |y(k)|.

When the envelope has the proper value the error p(k) will be zero, otherwise non-zero. The error carries sign information to indicate which direction the envelope is in error. The adaptive algorithm is defined by specifying a performance/cost/fitness function based on the error p(k) and then developing a procedure that adjusts the filter impulse response so as to minimize or maximize that performance function.

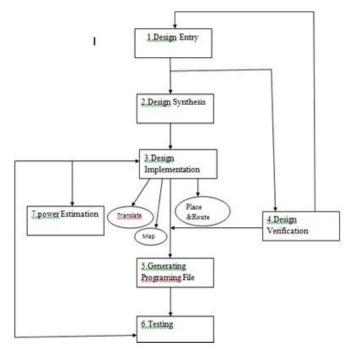

3.2 VHDL Design Flow Of Traversal FIR Filter

Fig 2: VHDL Flow of Transversal FIR filter design

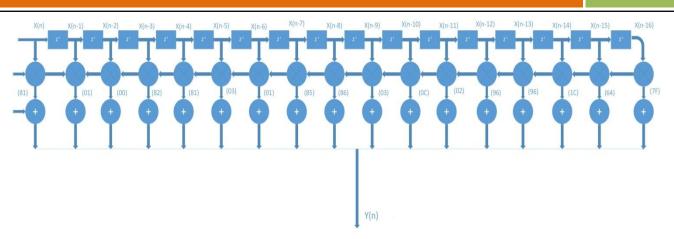

Fig 3: Architectural Diagram

#### 4. Result Analysis

The FIR filter has two basic structures: direct form and transpose form. The direct form has one huge addition at the end as shown in fig 1.The above figure shows that the output

of the FIR filter is obtained by performing the multiplication of individual delay line with their respective filter coefficients.

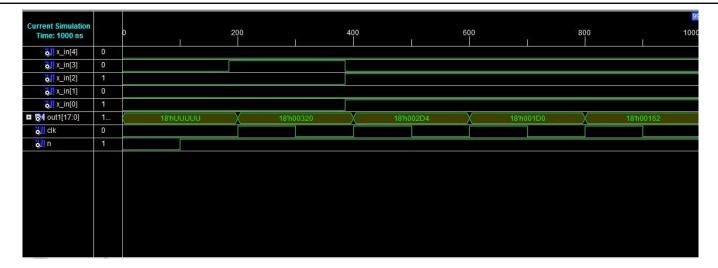

In our proposed method we have synthesized the FIR filter successfully using the ISE tool, the simulation results has been given below showing satisfactory output.

Synthesis

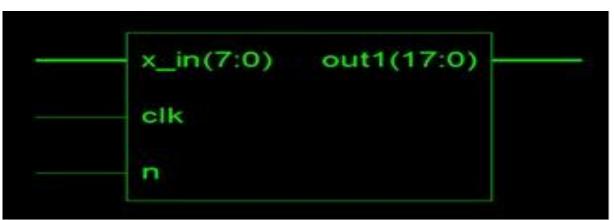

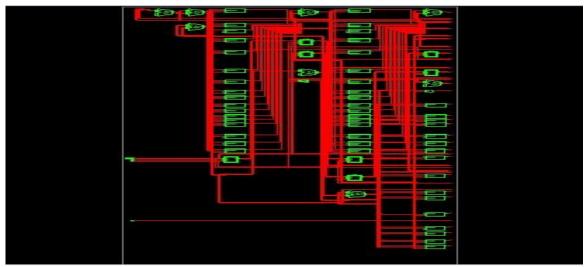

**Fig 4:** Block diagram of 16-Tap FIR filter.

Fig 5: RTL schematic of 16-Tap FIR filter

2015

#### Fig 6: Simulation Result

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |

| Number of Slices                              | 458  | 768       | 59%         |  |  |  |

| Number of Slice Flip Rops                     | 260  | 1536      | 16%         |  |  |  |

| umber of 4 input LUTs                         | 805  | 1536      | 52%         |  |  |  |

| Number of bonded IOBs                         | 28   | 124       | 22%         |  |  |  |

| Number of MULT18X18s                          | 4    | 4         | 100%        |  |  |  |

| Number of GCLKs                               | 1    | 8         | 12%         |  |  |  |

#### Fig 7: Device Utilization Summary

#### **Filter Equation**

FILTER LENGTH = 17 AS WE HAVE ONE TAP EQUAL TO ZERO,TOTAL NO. OF NON-ZERO TAPS=16 THE ORDER OF AN FIR FILTER =16

2015

| Power Sumn   | nary       |

|--------------|------------|

| Optimization | None       |

| Data         | Production |

| Quiescent(W) | 0.032      |

| Dynamic (W)  | 0.003      |

| Total (W)    | 0.035      |

|              |            |

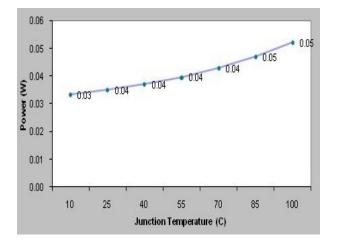

Fig 8: Power Summary

Fig 10: power Vs Temp.

#### 5. Conclusion

This paper presents a traversal FIR filter system Algorithm which has flexibility, power-efficiency and configuration time advantages. This project includes ripple carry adder and multiplier with its regular and parallel structure which can be realized easily on silicon as well leads to a reduction in hardware cost. The FIR filter is coded using VHDL and further it is Synthesized using the tool and simulation is done using ISE Xilinx9.2i Simulator.The presented FIR filter system is responsible for providing the best solution for realization and autonomous adaptation of FIR filters, and can be used in many communication and Digital signal processing applications like Channel Equalization, Adaptive noise cancellation, Adaptive echo cancellation, System identification and many others.

| Source               | Voltage | Power<br>(W) | Icc (A) | lcca (A) |

|----------------------|---------|--------------|---------|----------|

| VCONT                | 12      | 0.013        | 0.003   | 0.008    |

| VCCAUX               | 2.5     | 0.020        | 0.000   | 0.008    |

| V <sub>cco</sub> 3.3 | 3.3     | 0.000        | 0.000   | 0.000    |

| V <sub>cco</sub> 2.5 | 2.5     | 0.002        | 0.000   | 0.001    |

| V <sub>cco</sub> 1.8 | 1.8     | 0.000        | 0.000   | 0.000    |

| V <sub>cco</sub> 1.5 | 1.5     | 0.000        | 0.000   | 0.000    |

| V <sub>cco</sub> 1.2 | 12      | 0.000        | 0.000   | 0.000    |

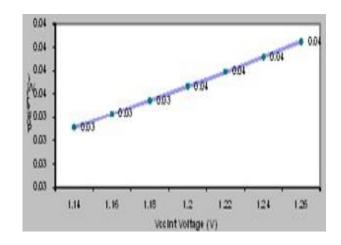

Fig 9: Voltage Source Information

Fig 11: Power Vs Voltage.

#### References

- 1. Haykin, Simon, Adaptive Filter Theory, Prentice Hall, Upper Saddle River, New Jersey, 1996.

- Abul Fazal Reyas Sarwar1, Saifur Rahman2, "Design of Multiplier Less 32 Tap FIR Filter using VHDL", International OPEN ACCESS Journal Of Modern Engineering Research, Vol. 4 Iss. 6 June. 2014.

- 3. Achinta Roy, "DESIGN OF 30-TAP FIR FILTER USING VHDL",2014.

- Fábio Fabian Daitx," VHDL Generation of Optimized FIR Filters", VHDL Generation of Optimized FIR Filters, 978-1-4244-2628-7/08/\$25.00 ©2008 IEEE.

- Yan Sun and Min Sik Kim," A High-Performance 8-Tap FIR Filter Using Logarithmic Number System", School of Electrical Engineering and Computer Science Washington State University.

- Mrs.Vidya H. Deshmukh, Dr. Abhilasha Mishra, Prof. Dr.Mrs.A.S.Bhalchandra, "FIR Filter Design on Chip Using VHDL", IPASJ International Journal of Computer Science (IIJCS), Volume 2, Issue 7, July 2014

- Deepshikha Bharti #1, K. Anusudha\*2," High Speed FIR Filter Based on Truncated Multiplier and Parallel Adder", International Journal of Engineering Trends and Technology (IJETT) – Volume 5 Number 5 -Nov 2013.

#### **Author Profile**

**Ms. Soumee Sharmeela Pattnaik** perusing M.Tech from Centurion University Of Technology & Management and Completed B.Tech from Krupajal Engineering College in the year 2013.

**Mr. Ritisnigdha** Das was born on 9th july, 1982. He received the B.Tech degree in Applied electronics and Instrumentation engineering from ITER under Biju pattanaik university and Technology in 2007 and M.Tech degree in Vlsi and Embedded design from centre for microelectronics, CET (BPUT), Odisha in 2010.Currently he is working as Asst. Professor at Centurion University of Technology and management , Bhubaneswar, Odisha. He has also 4 years of teaching experience in Electronics and communication engineering.

His research area of interest includes implementation of analog, digital circuits in CMOS

technology, VLSI implementation of Vedic mathematics.

Mr. Siba Kumar Panda was born on November 09,1989. He received the B.Tech degree in Electronics & Communication Engineering from Biju Patnaik University of Technology, odisha in 2012 and M.Tech degree in VLSI Signal Processing Specialization from Veer Surendra Sai University Of Technology, odisha in 2014. Currently he is working as an Assistant Professor at Centurion University of Technology and Management, Bhubaneswar, Odisha. He also awarded the University Silver medal for best Electronics & Telecommunication Engineering Post Graduate for the academic year 2012-2014 at VSSUT, Odisha. His research area of interest includes Ultrawideband (UWB) device design, RF circuit design

using CMOS Technique, VLSI implementation of Vedic Mathematics, VLSI Signal Processing.